M R S Internet Journal of

Nitride Semiconductor Research

Volume 9, Article 7

### The Ambient Temperature Effect on Current-Voltage Characteristics of Surface-Passivated GaN-Based Field-Effect Transistors

<u>W.L. Liu, V.O. Turin, A.A. Balandin</u> Nano-Device Laboratory, Department of Electrical Engineering, University of California - Riverside

Y.L. Chen, K.L. Wang Device Research Laboratory, Electrical Engineering Department, University of California - Los Angeles.

This article was received on Friday, September 3, 2004 and accepted on Friday, November 19, 2004.

#### Abstract

We have studied experimentally the effect of ambient temperature on performance of the surface-passivated  $Al_{0.2}Ga_{0.8}N/GaN$  heterostructure field-effect transistors in the temperature range from 25°C to 250°C. The measured data have been compared with physics-based modeling of the GaN transistor characteristics under different ambient temperatures. The experimental data, showing about 33% degradation in the saturation current with a temperature increase from 25°C to 250°C, agrees well with the results of simulations performed using ISE DESSIS software. Obtained results and analytical extrapolations can be used for predicting device performance in changing environments, as well as for optimization of the device structure.

#### 1. Introduction

GaN-based heterostructure field-effect transistors (HFETs) are attracting attention as promising candidates for high-frequency high-power applications. AlGaN/GaN HFETs have demonstrated the ability to operate at frequencies above 10 GHz while providing power levels exceeding 11 W/mm [1] [2]. These devices are capable of working with low flicker noise levels (Hooge parameter  $\alpha_{\rm H} \approx 10^{-4} \sim 10^{-5}$ ) comparable to those in Si and GaAs devices [3] [4]. For applications in remotely controlled vehicles and satellites, the stability of device operation under changing temperature is of critical importance. An increase in ambient temperature coupled with strong self-heating effects in high-power GaN transistors may result in significant performance degradation. The thermal structure resistance also increases at high temperature due to the decrease of the thermal conductivity *K*, which falls off as ~  $1/T^{0.5}$  in GaN films [5] [6] [7]. In this paper we report results of experimental investigation and computer simulation of the effect of ambient temperature on performance of the SiO<sub>2</sub>-passivated Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN HFETS.

#### 2. Experiment

The Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN heterostructure was grown on a semi-insulating SiC substrate by metal organic chemical vapor deposition technology. The structure consists of 1.2 µm undoped GaN, 50 nm undoped GaN channel layer, 3 nm undoped Al<sub>0.2</sub>Ga<sub>0.8</sub>N spacer and 15 nm Si doped ( $N_{\rm D}$ =6×10<sup>18</sup>cm<sup>-3</sup>) Al<sub>0.2</sub>Ga<sub>0.8</sub>N barrier layers. HFETs with gate dimension of 1 µm × 20 µm, and the gate-source and gate-drain distances of 1 µm have been fabricated on this heterostructure. Mesa isolation is achieved by ion implantation of As<sup>+</sup> at 75 keV and dose1.27×10<sup>11</sup> cm<sup>2</sup>, As<sup>+</sup> at 375 keV and dose 4.32×10<sup>11</sup> cm<sup>2</sup>, and He<sup>+</sup> at 75 keV and dose 5.43×10<sup>11</sup> cm<sup>2</sup>. The source - drain ohmic contacts are formed by Ti/Al/Ni/Au (200Å /400Å /1500Å) multilayer. The gate Schottky contact is formed by Pd/Au (200Å/6500Å) layer. Before metal

deposition,  $O_2$  descum and BOE etching were conducted on the Schottky area to remove residues and the thin oxide layer. After the above processes are finished, a 270 nm SiO<sub>2</sub> layer was deposited by plasma enhanced chemical vapor deposition to provide surface passivation. The transistor current-voltage (IV) characteristics were measured using a HP4142B-based parameter analyzer connected to the Signatone probe station with a hot chuck.

#### 3. Physics-Based Modeling

The physics-based ISE DESSIS software has been used for simulation of the temperature dependent IV characteristics of the GaN-based field-effect transistors. The physical parameters defining the electron and thermal transport properties of GaN material have been taken from recently published works [5] [8] [9] [10] [11] [12] [13]. For simplicity the 2D simulations were carried out for a metal-semiconductor field-effect transistor with the following parameters: the doping concentration in the active layer is  $3 \times 10^{17}$  cm<sup>-3</sup>; the thickness of the active layer is 200 nm. The source - drain separation  $L_{\text{SD}} = 3 \,\mu\text{m}$  and the gate length  $L_{\text{G}} = 1 \,\mu\text{m}$  are chosen to be the same as in the actual transistors under test. The active n-GaN channel is on the top of 3  $\mu\text{m}$  thick semi-insulating GaN buffer layer. The device structure was assumed to be on a 300  $\mu\text{m}$  thick SiC substrate. The simulation domain size along the substrate was 1500  $\mu\text{m}$ . We have adopted the low-field mobility model from Ref. [8]. The high-field mobility has been calculated using the Canali model [9]:

$$\mu_{high} = \mu_{low} / \left( 1 + \left( \mu_{low} E / \upsilon_{sol} \right)^{\beta_0} \right)^{1/\beta_0}$$

(1)

The electron saturation velocity  $v_{sat} = 1.91 \times 10^7$  cm/s at 300 K was extracted from the Monte-Carlo simulation results [10]. The coefficient for the linear dependence of the saturation velocity on temperature was assumed to be -6.33 × 10<sup>3</sup> cm/s K. This parameter was obtained by fitting the data from the Monte Carlo simulations reported in [11].

The basic equations used in the drift-diffusion model (DDM) simulation include Poisson, electron continuity, hole continuity and thermal conductivity equations

$$\begin{cases} \nabla_{E} \cdot \nabla \varphi = -e(p - n + N_{D} - N_{A}) \\ \frac{\partial n}{\partial t} = \frac{1}{e} \nabla \cdot \vec{j}_{n} + G_{n} - R_{n} \\ \frac{\partial p}{\partial t} = -\frac{1}{e} \nabla \cdot \vec{j}_{p} + G_{p} - R_{p} \\ c \frac{\partial T}{\partial t} - \nabla \cdot k(T) \nabla T = -\nabla \cdot \left(\phi_{n} \vec{j}_{n} + \phi_{p} \vec{j}_{p}\right) \end{cases}$$

$$(2)$$

The current densities for electrons and holes are given as

$$\vec{j}_n = -nq\mu_n \nabla \phi_n$$

$$\vec{j}_p = -pq\mu_p \nabla \phi_p$$

(3)

In the above equations we adopted the standard notations in their conventional meaning. For the electrical boundaries without contacts, the reflective boundary conditions are applied. For the Schottky contact, the boundary conditions are defined as

$$\varphi = V_{g} - \Phi_{B} + \frac{kT}{q} \ln\left(\frac{N_{C}(T)}{n_{i}}\right)$$

$$\vec{J}_{n} \cdot \vec{N} = q \upsilon_{n} \left(n - n_{0}^{B}\right)$$

$$\vec{J}_{p} \cdot \vec{N} = q \upsilon_{p} \left(p - p_{0}^{B}\right)$$

$$n_{0}^{B} = N_{C}(T) \exp\left(\frac{-q\Phi_{B}}{kT}\right)$$

$$p_{0}^{B} = N_{V}(T) \exp\left(\frac{-E_{G} + q\Phi_{B}}{kT}\right)$$

(4)

The Schottky barrier height  $\Phi_B$  is the difference between the metal work function and the electron affinity of the semiconductor. Here we assume it is equal to a typical value of 1 eV.  $n_0^B$  and  $p_0^B$  are the equilibrium electrons and holes densities at contact surface, respectively. The values for the thermionic emission velocities  $v_n$  and  $v_p$  are  $2.573 \times 10^6$  cm/s and  $1.93 \times 10^6$  cm/s respectively. To close the thermal equation, the isothermal boundary condition is assumed for the bottom of the substrate, where the temperature is equal to that of ambient, and the adiabatic boundary is assumed for the top and lateral surface. Room temperature thermal conductivities for SiC and GaN are taken from Ref. [12]. The  $T^{-0.5}$  temperature dependence for thermal conductivity of GaN [5] [6] [7] and  $T^{-1}$  for SiC [12] has been adopted in the simulations. The details of the simulation approach based on the solution of the carriers drift-diffusion and thermal diffusion equations were described elsewhere. [13] A posterior comparison with experiments attests that the simplified model for the transistor is capable of capturing the main features of ambient heating effects in AlGaN/GaN HFETs.

#### 4. Results

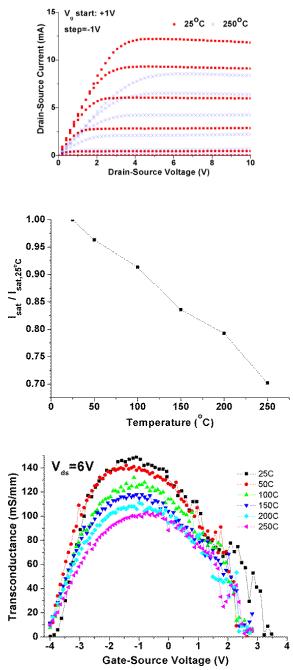

In Figure 1 we present typical measured DC IV characteristics of SiO<sub>2</sub>-passivated Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN HFET with the gate bias changing from 1V to - 4V. The data is shown for two ambient temperatures T=25°C and T=250 °C. One can see the reduction of the current with increased ambient at each value of the gate bias. The saturation current reduction is caused by degradation of the electron mobility due to increased electron - phonon scattering. The decrease of the saturation current at zero gate bias when temperature increases to 250 °C is about 33%. Figure 2 shows the saturation current as a function of temperature at  $V_g$ =0V. The saturation current is normalized to its room-temperature value. In the examined range of temperatures the decrease is linear and can be approximated as  $I_{sat}/I_{sat}(T=25^{\circ}\text{degree}; C)=1.03-0.0013 \cdot T$ , where T is measured in 9decreaseC

in <sup>o</sup>degree;C.

The experimental dependence of the transconductance on ambient temperature is presented in Figure 3. For tested HFETs the maximum transconductance is achieved at about  $-1V \sim -2V$ , while the threshold voltage is about -4V. One observes that as the ambient temperature increases the transconductance peak decreases and shifts toward the lower bias voltage. Compared with the room-temperature value, the maximum transconductance at  $250^{\circ}$  degree;C decreases by  $\sim 33$  percent. The small shift in the peak position can be attributed to some increase in the gate leakage current. The gate metal Pd/Au contact used in the tested devices showed very good thermal stability over the measured temperature range.

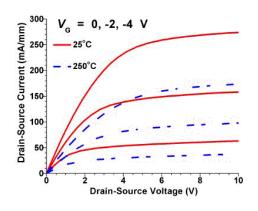

In order to estimate the reliability of the system, it is important to be able to predict changes in transistor IV characteristics with varying ambient temperature. The results of the computer simulation of IV characteristics of GaN-based transistor for  $T=25^{\circ}$  degree; C and  $T=250^{\circ}$  degree; C are shown in Figure 4 with the solid and dashed curves, respectively. Comparing with Figure 1, one can see that the degradation trend in the saturation current is captured by the simulation results very well. The change in the current value with temperature increase to  $250^{\circ}$  degree; C is about 36%, which is very close to experimentally observed decrease.

#### 4.1. Conclusions

We investigated the effect of ambient temperature on the performance of the SiO2-passivated Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN HFETs in

the temperature range from  $25^{\circ}$ C to  $250^{\circ}$ C. The experimental data indicates ~33% degradation in the saturation current and transconductance with temperature increase to  $250^{\circ}$  degree;C. The results of computer simulations performed using the ISE DESSIS software with GaN parameters and material-specific models for the carrier and heat transport are in good agreement with the experimental data. Obtained experimental dependencies and modeling approach can be used for predicting GaN-based device performance under changing ambient temperature.

# Acknowledgments

The research in UCR was supported by the ONR Young Investigator Award N000140210352 to A.A.B.

References

## References

[1] U. K. Mishra, P. Parikh, Y. -F. Wu, Proc. IEEE 90, 1022-1031 (2002).

[2] S. J. Pearton, J. C. Zolper, R. J. Shul, F. Ren, J. Appl. Phys. 86, 1 (1998).

[3] A. Balandin, Electron. Lett. 36, 912 (2000).

[4] M. E. Levinshtein, S. L. Rumyantsev, R. Gaska, J. W. Yang, M. S. Shur, Appl. Phys. Lett. 73, 1089-1091 (1998).

[5] J. Zou, D. Kotchetkov, A. A. Balandin, D. I. Florescu, F. H. Pollak, J. Appl. Phys. 92, 2534-2539 (2002).

[6] D. Kotchetkov, J. Zou, A. A. Balandin, D. I. Florescu, F. H. Pollak, Appl. Phys. Lett. 79, 4316 (2001).

[7] K.A. Filippov, A.A. Balandin, MRS Internet J. Nitride Semicond. Res. 8, 4 (2003).

[8] T. T. Mnatsakanov, M. E. Levinshtein, L. I. Pomortseva, S. N. Yurkov, G. S. Simin, M. A. Khan, Sol. St. Electr. 47, 111-115 (2003).

[9] C. Canali, G. Majni, R. Minder, G. Ottaviani, IEEE Trans. Electr. Dev. ED22, 1045-1047 (1975).

[10] M. Farahmand , IEEE Trans. Electr. Dev. 48, 535-542 (2001).

[11] U. V. Bhapkar, M. S. Shur, J. Appl. Phys. 82, 1649-1655 (1997).

[12] S. T. Allen, S. T. Sheppard, W. L. Pribble, R. A. Sadler, T. S. Alcorn, Z. Ring, J. W. Palmour, *Mater. Res. Soc. Symp. Proc.* 572, 15-22 (1999).

[13] V. O. Turin, A. A. Balandin, Electron. Lett. 40, 81-83 (2004).

**Figure 1**. Current-voltage characteristics of the surface-passivated AlGaN/GaN HFET at two different ambient temperatures 25°C (squares) and 250°C (crosses), respectively.

Figure 2. Measured saturation current at  $V_g=0V$  as a function of the ambient temperature. The data are normalized to the current value at room temperature.

**Figure 3**. Measured transconductance as a function of the gate bias at different ambient temperature.

**Figure 4**. Simulated current-voltage characteristics for GaN-based field-effect transistor at two different temperatures 25°C (solid curves) and 250°C (dashed curves), respectively.

$\ensuremath{\mathbb{C}}$  2004 The Materials Research Society

Nitride Semiconductor Research